据美国半导体技术机构SemiAnalysis所发布的专栏报告指出,日本佳能的纳米压印(NIL)技术在国际芯片领域被冠以“匹敌甚至超过EUV的能力”,从理论上来说,纳米压印可以达到甚至是超过EUV光刻机的曝光分辨率,并且设备的制造成本比EUV光刻机更低。

但是纳米压印技术存在多种问题,例如零件的损耗、多层图案的对齐精度、制造逻辑芯片的良品率等问题。日本的纳米压印设备与ASML主导的传统光刻设备不同,尽管美国也对日本企业实施出口管制,但纳米压印设备还可以进行出口。

如果中国企业在EUV领域的进展缓慢,那么与日本佳能合作,尝试使用纳米压印技术制造芯片,也是一条可行的技术路线。

纳米压印光刻纳米压印与光学光刻的核心理念是一致的,都是将掩模板上面的图案转移到晶圆上面。先进行多层的图案化叠加,然后进入到刻蚀、沉积等工艺步骤,最终完成整个芯片之后进入封装环节。

只不过光学光刻使用光源透过光缝快速扫描印刷,而纳米压印则是使用一种特定的“印章”,将图案进行机械化印刷,这两种技术存在本质上的差别。

纳米压印技术,最早是由美国普林斯顿大学的华人科学家周郁在1995年提出的技术。

2001年,纳米压印从学术界逐步过渡到商业化的范畴,成立了分子压模公司 (Molecular Imprints Inc.),开始将纳米压印技术应用在制造半导体芯片上。

2014年,在日本佳能公司收购了分子压模公司之后,又联合了日本印刷株式会社、铠侠控股等多个企业共同开发纳米压印的芯片制造技术。并且佳能将纳米压印技术定义为ASML EUV的替代方案,企图用这种方法来缩短与ASML的技术差距。

目前为止,全球的芯片制造格局变成了ASML、尼康、佳能三家比拼,中国企业紧随其后。

ASML持有浸润式DUV光刻机和EUV光刻机这两大王牌设备,尼康走的是传统光刻,旗下有干式DUV和浸润式DUV设备,但设备的技术水平落后于ASML。佳能拥有干式DUV光刻机,并且还持有已经商用的纳米压印设备。

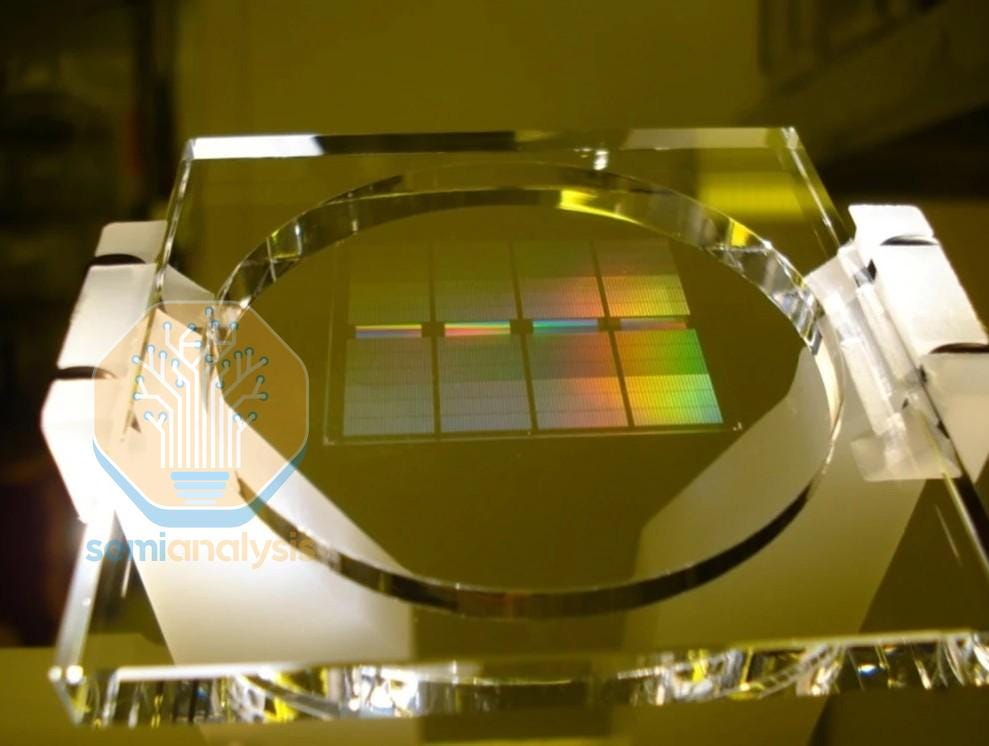

2023年10月13日,佳能宣布推出型号为“FPA-1200NZ2C”纳米压印光刻机设备。据佳能表示,该设备的硬件能力支持最小线宽14nm的芯片制造,相当于是逻辑芯片的5nm节点。随着掩模技术的提升,该设备可以实现2nm节点的逻辑芯片制造,并且其技术成本要比ASML的EUV设备低很多。

现存问题

现存问题佳能的纳米压印设备已经交付给了铠侠集团和镁光科技,用于制造闪存芯片。存储芯片与逻辑芯片存在本质上差别,存储芯片的结构简单,重复度高,对于掩模的要求较低,甚至几百层的图案结构都是一致的。而逻辑芯片涉及到CPU、GPU、NPU等多种晶体管的图案设计,其每层的电路图案都不一样,这对于掩模和设备精度要求很高。

纳米压抑的机械印章非常细小,其尺寸相当于人类头发的横截面。现在使用这个设备每秒压印一次芯片,只要是机械印章出现一丁点的缺陷或者是损耗,这都会直接影响芯片的良品率。

传统光学光刻所使用的掩模板,其使用寿命支持光刻100000个晶圆,而纳米压印所使用的掩模板寿命远低于光学掩模板。想要解决这个问题,就必须投入资源去开发适配的材料,不但成本高,而且耗时长,这也是纳米压印迟迟没有制造逻辑芯片的原因之一。

我们将目光投向中国大陆市场,杭州璞璘是中国唯一一家深耕纳米压印技术的企业,由该公司制造的PL-SR系列纳米压印设备已经在2025年8月份正式交付给客户使用。并且该公司的创始人葛海雄先生,师从纳米压印技术发明人周郁博士,具备20年以上的技术开发经验。

根据璞璘公司的资料显示,该设备是迄今为止唯一在国内初步实现20nm以下高端芯片所需的纳米压印设备。并且公司还向市场供应了包括模板复制胶、耐刻蚀型纳米压印胶、刻蚀传递胶、光学纳米压印胶、耐腐蚀纳米压印胶、增粘胶、防粘试剂在内的40余种制造材料,建立起一条全新的芯片产业链。

佳能在硬件设备上,对比我国现存的产品具备明显优势。

但中国企业的路线是押注传统光学光刻和纳米压印光刻两种技术路线,并且这两种技术路线并行研发。在无法获取EUV设备的前提下,纳米压印技术是一个可以尝试的技术方案,但纳米压印现存的问题就是制造先进逻辑芯片的损耗大、良品率低,可以当做备选方案,光学光刻技术依然是主流的选择。